## ЭЛЕКТРОНИКА И РАДИОТЕХНИКА

УДК 621.389

## ОПИСАНИЕ ПРОТОТИПА СЧИТЫВАЮЩЕЙ ЭЛЕКТРОНИКИ ДЛЯ ЕМКОСТНЫХ ДЕТЕКТОРОВ

© 2024 г. Э. В. Аткин<sup>а, \*</sup>, Д. Д. Норманов<sup>а</sup>, С. И. Ямалиев<sup>а</sup>, А. Р. Серазетдинов<sup>а</sup>, А. А. Солин<sup>b, \*\*</sup>, Е. А. Усенко<sup>c, \*\*\*</sup>

<sup>а</sup>Национальный исследовательский ядерный университет "МИФИ" Россия, 115409, Москва, Каширское ш., 31

<sup>b</sup>Институт ядерных проблем Белорусского государственного университета Беларусь, 220006, Минск, ул. Бобруйская, 11

<sup>с</sup>Институт ядерных исследований Российской академии наук Россия, 117312, Москва, просп. 60-летия Октября, 7а

> \*e-mail: evatkin@mephi.ru \*\*e-mail: solin@hep.by \*\*\*e-mail: Eugueni.oussenko@cern.ch

Поступила в редакцию 07.12.2023 г. После доработки 17.05.2024 г. Принята к публикации 06.06.2024 г.

Представлено описание прототипа считывающей электроники для емкостных детекторов на основе специализированной интегральной микросхемы (СИМС), разработанной специально для съема и предварительной обработки сигналов с плоских резистивных камер эксперимента SPD на строящемся коллайдере НИКА ОИЯИ (г. Дубна). Восьмиканальная микросхема оптимизирована для работы с детекторами, имеющими характеристический импеданс считывающих электродов в диапазоне 35-110 Ом при приведенном ко входу эквивалентном малом шумовом заряде не более 2500 электронов. В СИМС предусмотрены регулировки порога по величине приведенного ко входу заряда в диапазоне 10-450 фКл, гистерезиса пороговой характеристики в диапазоне 0-12%, а также времени расширения сигнала в диапазоне 0.5-100 нс. Схема была оптимизирована для уменьшения джиттера по переднему фронту (менее 10 пс) и энергопотребления (менее 25 мВт на один канал). Представлены структурная и электрическая схемы, показаны результаты моделирования ключевых сложно-функциональных блоков и общий вид топологии спроектированной СИМС.

## DOI: 10.31857/S0032816224050093 EDN: ETUEEI

## 1. ВВЕДЕНИЕ

Современное поколение экспериментов на ускорительных комплексах требует увеличения числа каналов считывающей электроники и в целом повышения степени интеграции в первую очередь из-за значительно возросшей гранулярности детекторов. Это сопровождается ужесточением требований по многим аспектам, в том числе к функциональной сложности накамерной электроники, что может быть в полной мере реализовано только с использованием специализированных интегральных схем.

В данной статье представлена разработка специализированной интегральной микросхемы (СИМС) для создания накамерной электроники эксперимента SPD (Spin Physics Detector) на строящемся коллайдере НИКА.

Развитие проектов и процессов проектирования полупроводников позволяет совершить важные сдвиги в развитии электроники. При этом разработка процессов КМОП (комплементарная структура металл—оксид—полупроводник) и передовых технологий разварки кристаллов с низким уровнем паразитных

связей является одним из таких важных достижений, обеспечивающих переход к современным многоканальным электронным системам считывания.

Данная СИМС будет использоваться при создании накамерной электроники для плоских резистивных камер, времяпролетных измерений, а также для других применений. Микросхема оптимизирована для работы с детекторами, имеющими характеристический импеданс считывающих электродов в диапазоне 35-110 Ом, а также приведенный ко входу эквивалентный шумовой заряд не более 2500 электронов. В СИМС предусмотрены регулировки порога в диапазоне 10-450 фКл по значению приведенного ко входу заряда, а также времени расширения сигнала в диапазоне 0.5–100 нс. Схема была оптимизирована для уменьшения джиттера по переднему фронту (менее 10 пс) и энергопотребления (менее 25 мВт на один канал).

В задачи СИМС входят выполнение аналогового дифференциального считывания заряда с детектора частиц и дискриминация сигнала постоянным порогом, растяжение длительности импульса с сохранением пропорциональности ширины импульса от величины входного заряда, формирование выходных сигналов в различных стандартах, в том числе в уровнях LVDS (низковольтная дифференциальная передача сигналов), а также выработка сигнала ИЛИ по всем восьми каналам. В считывающей электронике, предназначенной для амплитудных измерений, существуют несколько известных подходов к измерению заряда - аналоговое пиковое детектирование, использование высокоскоростного сканирующего АЦП и использование метода преобразования заряда

во временной интервал. В представленной микросхеме используется последний метод, который дает возможность измерения амплитуды сигнала по его длительности. При этом передний фронт импульса несет точную временную информацию, а ширина импульса пропорциональна входному заряду [1, 2].

## 2. СТРУКТУРА МИКРОСХЕМЫ

В рамках продолжения работ по разработке микросхем для электроники физического эксперимента [3—6] представленная СИМС предназначена для съема и предварительной обработки сигналов с плоских резистивных камер (RPC) детекторов для эксперимента SPD на строящемся коллайдере тяжелых ионов НИ-КА, ОИЯИ (г. Дубна). Она содержит 8 каналов усилителей-дискриминаторов с функцией преобразования заряда во временной интервал.

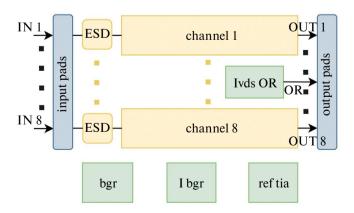

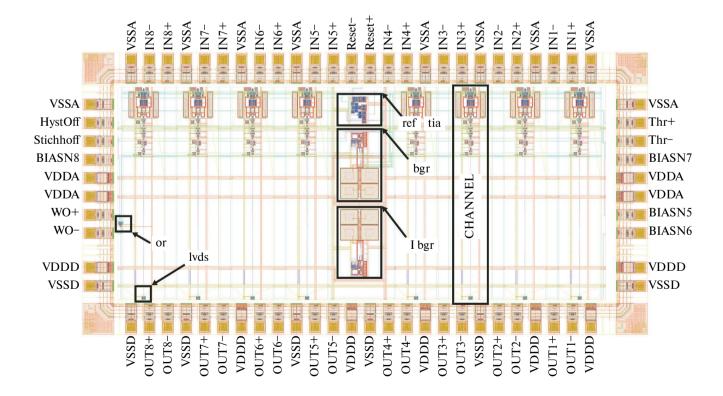

В состав СИМС вошли следующие блоки (см. рис. 1):

- 1) ref tia блок управления входным импедансом;

- 2) BGR блок формирования опорных потенциалов для 8 каналов;

- 3) IBGR блок задания дополнительного опорного тока для 8 каналов (в связи с наличием свободного пространства он сделан путем конфигурации bgr 600 900 1300 1400);

- 4) блок LVDS OR блок сборки сигналов по логике ИЛИ.

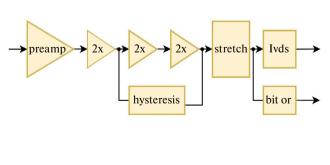

Структурная схема отдельного канала представлена на рис. 2. Канал состоит из блоков предусилителя (preamp), дифференциальных усилительных каскадов (2x), блока расширителя

Рис. 1. Структура микросхемы.

Рис. 2. Структурная схема одного канала.

импульсов (stretch), блока драйвера стандарта LVDS, блока гистерезиса (hysteresis) и бита или (bit or).

Канал предназначен для работы с катоданодным разностным сигналом без средней точки (заземления), для него предусмотрена подстройка входного сопротивления с учетом волнового сопротивления RPC (около 50–60 Ом). Дискриминатор спроектирован со встроенным программируемым гистерезисом. Сигналы с дискриминатора поступают на расширитель выходного импульсного сигнала по заднему фронту с программированием по длительности.

## 3. ОСОБЕННОСТИ СЛОЖНО-ФУНКЦИОНАЛЬНЫХ БЛОКОВ

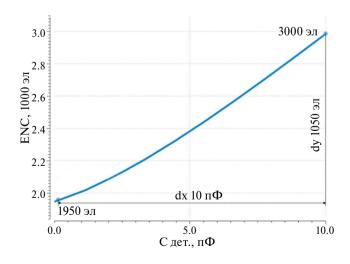

Ключевой особенностью схемы предусилителя и его реализации в составе канала является возможность подстройки входного сопротивления каналов схемы путем изменения сопротивления внешнего резистора. Таким образом достигается лучшее согласование сигналов в усилительном тракте и обеспечивается компромисс по отношению сигнал/шум. На рис. 3 приведена зависимость эквивалентного шумового заряда (в тысячах электронов) от входной емкости детектора. Зависимость описывается формулой

ENC =

$$1.956 + 102 \cdot эл. / пФ$$

.

Факторами, влияющими на эквивалентный шумовой заряд, являются режимы работы

входных транзисторов и транзисторов источника тока в трансимпедансном усилителе.

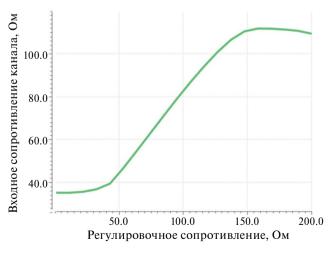

Блок подстройки входного сопротивления обеспечивает возможность согласования входного сопротивления усилительного тракта и сопротивления источника сигнала (см. рис. 4). Функциональным аналогом является схема, разработанная в ЦЕРН [1]. Для диапазона изменений сопротивления внешнего резистора от 40 до 80 Ом зависимость входного сопротивления канала имеет линейный характер, что позволяет согласовать его с сопротивлением источника сигнала. Блок подстройки представляет из себя линейный регулятор, ко входу которого подключается внешний резистор с сопротивлением, эквивалентным входному сопротивлению канала, а на выходе этого регулятора выдаются выходные режимные потенциалы источника тока трансимпедансного усилителя.

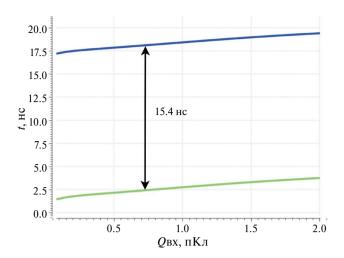

Схема расширителя устроена таким образом, чтобы была возможность плавного регулирования времени расширения сигнала от 0.5 до 100 нс. Она представляет собой дифференциальный вариант схемы, представленной в одном из последних прототипов микросхемы PADI [7]. Таким образом, можно добиться фиксированного расширения сигнала при всем динамическом режиме работы предусилителя (рис. 5).

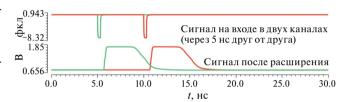

За счет плавной регулировки этого тока через внешний потенциал происходит расширение сигнала в указанном диапазоне (см. рис. 6). Также предусмотрена возможность его отключения,

**Рис. 3.** Эквивалентный шумовой заряд в зависимости от емкости детектора.

**Рис. 4.** Зависимость входного сопротивления от сопротивления регулирования.

в таком случае сигнал после каскадов усилителей, минуя расширитель, идет на вход LVDS-блока.

Блок ИЛИ собирает выходные сигналы блоков bitOR с восьми каналов СИМС. Таким образом, при наличии сигнала хотя бы в одном канале на выход ИЛИ будет передан импульс этого канала. В случае одновременного срабатывания нескольких каналов СИМС на выходе ИЛИ первый из пришедших импульсов сформирует передний фронт, а задний фронт сформирует сработавший канал с наибольшим зарядом.

Соответствие выходных уровней СИМС стандарту LVDS (или другим стандартам) осуществляется выбором соответствующих значений внешних сопротивлений нагрузки выходного каскада СИМС, а также заданием расчетного значения тока выходного каскада. Величина тока выходного каскада управляется внешним напряжением на соответствующем выводе СИМС. Блоки LVDS позволяют регулировать выходной ток в широком диапазоне, таким образом, схема может работать как в стандарте LVDS, так и в стандарте СМL (Current Mode Logic).

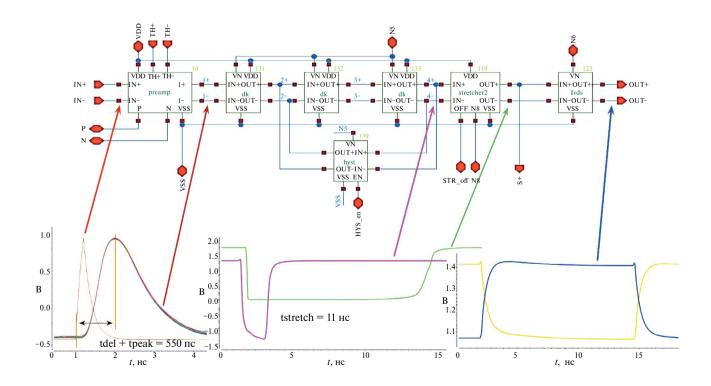

На рис. 7 показаны типовые диаграммы сигналов в основных точках.

**Рис. 5.** Зависимость длительности импульса на выходе усилительных каскадов (зеленый) и расширителя (синий) в зависимости от входного заряда.

**Рис. 6.** Диаграмма сигналов на выходе расширителя двух каналов.

Рис. 7. Форма типовых сигналов в канале микросхемы.

# 4. СИГНАЛЬНЫЙОТКЛИК И ПАРАМЕТРЫ СИМС

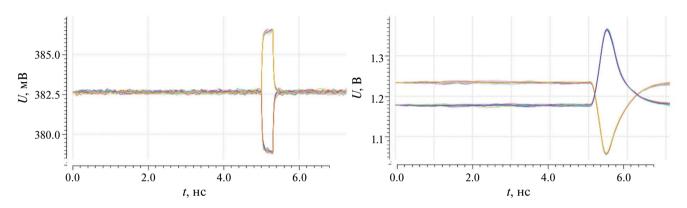

На вход микросхемы поступает заряд. Его величина соответствует площади под левым графиком рис. 8, поделенной на входное сопротивление. На правом графике изображенотклик предусилителя.

На рис. 9 представлена топология микросхемы с контактными площадками. На ней обозначены все сложно-функцианальные блоки, а именно, источники напряжения и тока (BGR, IBGR)

для аналоговых каналов и выходных интерфейсов и аналоговые каналы усилителя-дискриминатора. Размер макета (без контактных площадок) 3450 × 1500 мкм<sup>2</sup>. Основные параметры микросхемы приведены в табл. 1.

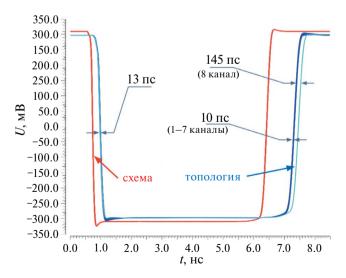

Моделирование импульсного отклика каналов после получения одинаковых сигналов на входах всех восьми каналов в типовом случае представлено на рис. 10. Экстракция показала, что один сигнальный отклик выбивается. Это могло быть следствием краевых эффектов.

**Рис. 8.** Диаграммы сигналов на входе канала и на выходе предусилителя при проведении временного шумового анализа.

Рис. 9. Топология всей микросхемы SPD NINO.

Таблица 1. Характеристики спроектированной СИМС

| Параметр                                       | Значение                   |

|------------------------------------------------|----------------------------|

| Технология                                     | КМОП, 180 нм, АО "Микрон"  |

| Напряжение питания, В                          | 1.8                        |

| Число каналов                                  | 8                          |

| Время нарастания переходной характеристики, пс | 500                        |

| Диапазон входных зарядов, фКл                  | 10-2000                    |

| Собственный временной джиттер, пс              | < 10                       |

| Шум при $C_{\text{дет}} = 0$ , е               | < 2000                     |

| Диапазон изменения входного гистерезиса, %     | 0-12                       |

| Межканальный кросс-ток, дБ                     | < 45                       |

| Ширина импульсов на входе расширителя, нс      | 0.5–3                      |

| Диапазон расширения импульсов на выходе, нс    | 0.5-100                    |

| Выходной каскад                                | Парафазный, открытые стоки |

| Размер кристалла микросхемы, мм <sup>2</sup>   | 2 × 4                      |

| Потребляемая мощность чипа, мВт                | 204                        |

Влияние краевых эффектов можно уменьшить, разместив реплики аналоговых каналов по краям. На рис. 10 красным отмечен сигнал на выходе при моделировании электрической схемы, а синим — на выходе экстрагированной топологии. Голубым отмечен экстрагированный выход восьмого канала, который отстает на 10 пс от остальных семи каналов.

**Рис. 10.** Импульсныйотклик на LVDS-выходе каналов микросхемы.

## 5. ЗАКЛЮЧЕНИЕ

В статье представлены результаты проектирования специализированной интегральной микросхемы SPD NINO. Микросхема предназначена для дифференциального съема и предварительной обработки сигналов от RPC-детекторов. Представлены разработанные схемы узлов и результаты их моделирования в пакете сквозного проектирования Саdence Virtuoso. Микросхема изготовлена на фабрике по КМОП-технологии с проектной нормой 180 нм АО "Микрон".

#### ФИНАНСИРОВАНИЕ РАБОТЫ

Работа выполнена при поддержке Министерства науки и высшего образования РФ (соглашение от 11.03.24 г. № 075-02-2024-1525) в рамках реализации федерального проекта "Подготовка кадров и научного фундамента для электронной промышленности" государственной программы "Научнотехнологическое развитие Российской Федерации". Производство интегральной микросхемы было выполнено при поддержке Министерства науки и высшего образования РФ в рамках федерального проекта "Подготовка кадров и научного фундамента для электронной промышленности" по государственному заданию на выполнение научно-исследовательской работы "Разработка методики

прототипирования электронной компонентной ба- 4. зы на отечественных микроэлектронных производствах на основе сервиса MPW (FSMR2023-0008)".

## СПИСОК ЛИТЕРАТУРЫ

- 1. Anghinolfi F., Jarron P., Krummenacher F., Usenko E., Williams M.C.S. // IEEE Trans. Nucl. Sci. 2004. V. 51. №. 5. P.1974. http://doi.org/10.1109/TNS.2004.836048

- Wong W.S., Alozy J., Ballabriga R. et al. // Radiat. Meas. 2020. V. 131. P. 106230. http://doi.org/10.1016/j.radmeas.2019.106230

- Atkin E., Azarov D., Ivanov P., Normanov D., Serazetdinov A., Shumikhin V. // Russ. Microelectron. 2022.

V. 51. P. 111. http://doi.org/10.1134/S1063739722020032

- Shumikhin V., Atkin E., Azarov D., Ivanov P., Normanov D., Serazetdinov A. // J. Phys. Conf. Ser. 2020.

V. 1690. № 1. P. 012068. http://doi.org/10.1088/1742-6596/1690/1/012068

- Atkin E., Azarov D., Ivanov P., Normanov D., Serazetdinov A., Shumikhin V. // J. Phys. Conf. Ser. 2020. V. 1690. P. 012072. http://doi.org/10.1088/1742-6596/1690/1/012072

- 6. Atkin E., Bulbakov I., Malankin E., Ivanov P., Normanov D., Petrovskiy S., Shumikhin V., Ivanov V., Voronin A., Samsonov V. // IEEE 30th International Conference on Microelectronics (MIEL). 2017. P. 225. http://doi.org/10.1109/MIEL.2017.8190108

- 7. Ciobanu M., Marghitu O., Constantinescu V. et al. // IEEE Trans Nucl Sci. 2021. V. 68. № 6. P. 1325. http://doi.org/10.1109/TNS.2021.3073487